EDA设计——在 ISE 软件中 使用 VHDL 语言实现 FIFO 存储器

本文共 2980 字,大约阅读时间需要 9 分钟。

1. 实验内容

FIFO实验与仿真验证。

2. 实验步骤

(1) 新建工程

(2) 新建VHDL Module文件;

(3) 编写VHDL文件,编译运行;

(4) 新建仿真文件VHDL Test Bench;

(5) 编写仿真文件;

(6) 编译运行,观看仿真图形;

(7) 得出实验结果,验证是否正确。

3. 实验结果

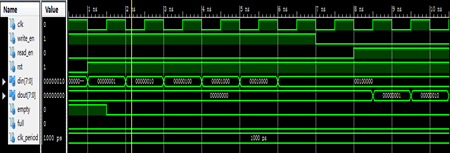

(1) 仿真激励

rst <= '0'; write_en <= '1'; wait for clk_period;rst <= '1'; din <= "00000001"; wait for clk_period;din <= "00000010"; wait for clk_period;din <= "00000100"; wait for clk_period;din <= "00001000"; wait for clk_period;din <= "00010000"; wait for clk_period;din <= "00100000"; wait for clk_period;write_en <= '0'; wait for clk_period; read_en <= '1'; wait for clk_period*10; read_en <= '0'; (2) 运行结果

4.代码附录

1.VHDL文件fifo.vhd

```clibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity fifo is port( clk : in std_logic; write_en : in std_logic; read_en : in std_logic; rst : in std_logic; din : in std_logic_vector(7 downto 0); dout : out std_logic_vector(7 downto 0); empty : out std_logic; full : out std_logic ); end fifo;architecture Behavioral of fifo is type fifo_array is array(0 to 63)of std_logic_vector(7 downto 0); signal fifo_memory : fifo_array; signal full_flag : std_logic; signal empty_flag : std_logic; signal read_add : std_logic_vector(5 downto 0); signal write_add : std_logic_vector(5 downto 0); signal counter : std_logic_vector(5 downto 0); beginprocess(rst,clk) begin if(rst='0') then dout<="00000000"; elsif(clk'event and clk='1') then if(read_en ='1'and empty_flag='0')then dout<=fifo_memory(conv_integer(read_add)); end if; end if;end process;process(clk) begin if(clk'event and clk='1')then if(rst='1'and write_en='1'and full_flag='0')then fifo_memory(conv_integer(write_add))<= din; end if; end if;end process;process(rst,clk) begin if(rst='0')then write_add<="000000"; elsif(clk'event and clk='1')then if(write_en ='1'and full_flag='0') then write_add <= write_add + 1; end if; end if;end process;process(rst,clk) begin if(rst='0') then read_add<="000000"; elsif(clk'event and clk='1') then if(read_en ='1'and empty_flag='0') then read_add <= read_add + 1; end if; end if;end process;process(rst,clk) variable temp : std_logic_vector( 1 downto 0 );begin if(rst='0')then counter<="000000"; elsif(clk'event and clk='1') then temp := read_en & write_en; case temp is when "00" => counter <= counter; when "01" => if( counter /= "111111" ) then counter <= counter + 1; end if; when "10" => if( counter /= "000000" ) then counter <= counter - 1; end if; when "11" => counter <= counter; when others => counter <= counter; end case; end if;end process;process( counter )begin if( counter = "000000" ) then empty_flag <= '1'; else empty_flag <= '0'; end if;end process;process( counter )begin if( counter = "111111" ) then full_flag <= '1'; else full_flag <= '0'; end if;end process;full <= full_flag;empty <= empty_flag;end Behavioral;转载地址:http://kute.baihongyu.com/

你可能感兴趣的文章

AcWing 798. 差分矩阵

查看>>

AcWing 828. 模拟栈

查看>>

AcWing 845. 八数码(BFS)

查看>>

AcWing 849. Dijkstra求最短路 I(Dijkstra)

查看>>

AcWing 4. 多重背包问题(带有个数限制的完全背包问题dp)

查看>>

EventBus简单Demo实现

查看>>

添加Selinux权限

查看>>

ifconfig网络配置信息解析

查看>>

(2019.9.10测试可用)如何在Windows的cmd中使用ls命令

查看>>

多因子策略中的IC、IR是什么,以及如何计算

查看>>

pd.resample('B')指重采样为工作日

查看>>

债券中的久期是什么意思

查看>>

MA、WMA、EMA、EXPMA区别及公式详述

查看>>

国内量化交易现状总结

查看>>

阿里云云解析DNS各种概念深度剖析

查看>>

(20200328已解决)从docker容器内复制文件到宿主机

查看>>

理解Docker ulimit参数

查看>>

Factor Exposure因子暴露

查看>>

理解DSL||AST||query clauses||X-Pack||JDBC||ODBC

查看>>

将DataFrame作为邮件正文HTML发送 in Python

查看>>